# LogiCORE™ IP SPI-4.2 Lite v4.3

## **User Guide**

UG181 June 27, 2008

Xilinx is disclosing this Document and Intellectual Property (hereinafter "the Design") to you for use in the development of designs to operate on, or interface with Xilinx FPGAs. Except as stated herein, none of the Design may be copied, reproduced, distributed, republished, downloaded, displayed, posted, or transmitted in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Any unauthorized use of the Design may violate copyright laws, trademark laws, the laws of privacy and publicity, and communications regulations and statutes.

Xilinx does not assume any liability arising out of the application or use of the Design; nor does Xilinx convey any license under its patents, copyrights, or any rights of others. You are responsible for obtaining any rights you may require for your use or implementation of the Design. Xilinx reserves the right to make changes, at any time, to the Design as deemed desirable in the sole discretion of Xilinx. Xilinx assumes no obligation to correct any errors contained herein or to advise you of any correction if such be made. Xilinx will not assume any liability for the accuracy or correctness of any engineering or technical support or assistance provided to you in connection with the Design.

THE DESIGN IS PROVIDED "AS IS" WITH ALL FAULTS, AND THE ENTIRE RISK AS TO ITS FUNCTION AND IMPLEMENTATION IS WITH YOU. YOU ACKNOWLEDGE AND AGREE THAT YOU HAVE NOT RELIED ON ANY ORAL OR WRITTEN INFORMATION OR ADVICE, WHETHER GIVEN BY XILINX, OR ITS AGENTS OR EMPLOYEES. XILINX MAKES NO OTHER WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DESIGN, INCLUDING ANY WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND NONINFRINGEMENT OF THIRD-PARTY RIGHTS.

IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOST DATA AND LOST PROFITS, ARISING FROM OR RELATING TO YOUR USE OF THE DESIGN, EVEN IF YOU HAVE BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. THE TOTAL CUMULATIVE LIABILITY OF XILINX IN CONNECTION WITH YOUR USE OF THE DESIGN, WHETHER IN CONTRACT OR TORT OR OTHERWISE, WILL IN NO EVENT EXCEED THE AMOUNT OF FEES PAID BY YOU TO XILINX HEREUNDER FOR USE OF THE DESIGN. YOU ACKNOWLEDGE THAT THE FEES, IF ANY, REFLECT THE ALLOCATION OF RISK SET FORTH IN THIS AGREEMENT AND THAT XILINX WOULD NOT MAKE AVAILABLE THE DESIGN TO YOU WITHOUT THESE LIMITATIONS OF LIABILITY.

The Design is not designed or intended for use in the development of on-line control equipment in hazardous environments requiring fail-safe controls, such as in the operation of nuclear facilities, aircraft navigation or communications systems, air traffic control, life support, or weapons systems ("High-Risk Applications"). Xilinx specifically disclaims any express or implied warranties of fitness for such High-Risk Applications. You represent that use of the Design in such High-Risk Applications is fully at your risk.

© 2005-2008 Xilinx, Inc. All rights reserved. XILINX, the Xilinx logo, and other designated brands included herein are trademarks of Xilinx, Inc. All other trademarks are the property of their respective owners.

## SPI-4.2 Lite v4.3 User Guide UG181 June 27, 2008

The following table shows the revision history for this document.

| Date    | Version | Revision                                                       |  |

|---------|---------|----------------------------------------------------------------|--|

| 8/31/05 | 1.1     | Initial Xilinx release.                                        |  |

| 1/18/06 | 1.2     | Updated release version, tool version, and release date.       |  |

| 7/13/06 | 2.0     | Updated version to 4.1, release date, ISE to v8.2i.            |  |

| 2/15/07 | 3.0     | Updated version to 4.2, ISE to v9.1i, added Virtex-3E support. |  |

| 4/02/07 | 3.1     | Added support for Spartan-3A DSP devices.                      |  |

| 4/16/08 | 4.0     | Updated for ISE v10.1.                                         |  |

| 6/27/08 | 4.5     | Updated the ISE v10.1 SP1 release.                             |  |

# Table of Contents

| Preface: About This Guide               |    |

|-----------------------------------------|----|

| Contents                                | 11 |

| Conventions                             | 12 |

| Typographical                           |    |

| Online Document                         | 13 |

| Chapter 1: Introduction                 |    |

| About the Core                          | 15 |

| Recommended Design Experience           | 15 |

| Additional Core Resources               |    |

| Technical Support.                      |    |

| Feedback                                |    |

| SPI-4.2 Lite Core                       |    |

| Document                                |    |

| Chapter 2: Core Architecture            |    |

| System Overview                         | 15 |

| Sink Core                               |    |

| Source Core                             |    |

| Sink Core Interfaces                    |    |

| Sink SPI-4.2 Interface                  |    |

| Sink User Interface                     | 22 |

| Source Core Interfaces                  | 30 |

| Source SPI-4.2 Interface                |    |

| Source User Interface                   | 32 |

| Chapter 3: Generating the Core          |    |

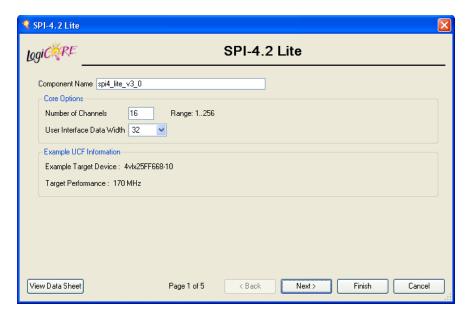

| CORE Generator Graphical User Interface | 43 |

| Main Screen                             | 44 |

| Sink Status Options Screen              |    |

| Calendar                                |    |

| Flow Control                            |    |

| Status Interface                        |    |

| Sink Other Options Screen               |    |

| Synchronization                         |    |

| Clocking.                               |    |

| Source Status Options Screen            |    |

| Calendar                                |    |

| Status Interface                        | 48 |

| Synchronization                         | 48 |

| Source Other Ontions Screen             | 48 |

|            | Bursting                                     |      |

|------------|----------------------------------------------|------|

|            | FIFO Threshold                               |      |

|            | Clocking                                     | 49   |

|            | Calendar COE File Format                     | . 50 |

| <b>O</b> l | uston A. Donings with the Orac               |      |

| Cna        | pter 4: Designing with the Core              |      |

|            | General Design Guidelines                    | . 51 |

|            | Know the Degree of Difficulty                |      |

|            | Understand Signal Pipelining                 |      |

|            | Keep it Registered                           |      |

|            | Recognize Timing Critical Signals            |      |

|            | Use Supported Design Flows                   |      |

|            | Make Only Allowed Modifications              |      |

|            | Initializing the SPI-4.2 Lite Core           |      |

|            | Sink Core                                    |      |

|            | Basic Operation                              |      |

|            | SPI-4.2 Interface                            |      |

|            | Sink User Interface                          |      |

|            | Sink Static Configuration Signals            |      |

|            | Sink Data Capture Implementation             |      |

|            | Synchronization and Start-up  Error Handling |      |

|            | · · · · · · · · · · · · · · · · · · ·        |      |

|            | Source Core                                  |      |

|            | Basic Operation                              |      |

|            | Source User Interface                        |      |

|            | Source Static Configuration Signals          |      |

|            | Synchronization and Start-up                 |      |

|            | Error Handling                               |      |

|            | O .                                          |      |

| Cha        | pter 5: Constraining the Core                |      |

|            | Overview                                     | gc   |

|            | Sink Core Required Constraints               |      |

|            | Timing Constraints                           |      |

|            | DCM and Static Alignment Constraints         |      |

|            | Placement Constraints                        |      |

|            | Sink Core Optional Constraints               |      |

|            | IDelayCtrl                                   |      |

|            | I/O Standards Constraints                    |      |

|            | Area Group Constraints                       |      |

|            | Timing Ignore Constraints                    |      |

|            | Source Core Required Constraints             |      |

|            | Timing Constraints                           |      |

|            | Placement Constraints                        |      |

|            | Source Core Optional Constraints             |      |

|            | I/O Standards Constraints                    |      |

|            | Area Group Constraints                       |      |

|            | Timing Ignore Constraints                    |      |

|            | User Constraints                             |      |

|            | COUL COMMITTED                               | * OC |

| Constraints Migration                           |     |

|-------------------------------------------------|-----|

| New Target Region or Device Package             |     |

| Modifying the UCF File                          | 109 |

|                                                 |     |

| Chapter 6: Special Design Considerations        |     |

| Sink Clocking Options                           | 111 |

| Embedded Clocking                               |     |

| User Clocking                                   |     |

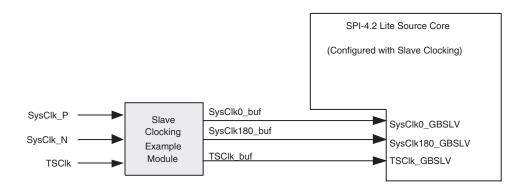

| Source Clocking Options                         |     |

| Master Clocking                                 |     |

| Slave Clocking                                  |     |

| Multiple Core Implementations                   |     |

| Instantiating Multiple Cores                    |     |

| Generating the Cores                            |     |

| Creating Top-Level UCF File                     |     |

| Clocking Considerations                         |     |

|                                                 |     |

| Chapter 7: Simulating and Implementing the Core |     |

|                                                 |     |

| Functional Simulation                           |     |

| Generating a Simulation Model                   |     |

| Timing Simulation                               |     |

| Synthesis                                       |     |

| Synthesis of Example Design                     | 127 |

| Xilinx Tool Flow                                | 128 |

| Example Design Script                           |     |

| NGDBuild                                        |     |

| Mapping the Design                              |     |

| Place and Route                                 |     |

| Static Timing Analysis                          |     |

| Timing Simulation                               |     |

| Generating a Bitstream                          | 129 |

|                                                 |     |

| Appendix A: SPI-4.2 Lite Control Word           |     |

|                                                 |     |

| Appendix B: SPI-4.2 Lite Calendar Programming   |     |

|                                                 |     |

| Overview                                        | 133 |

| Example 1                                       | 133 |

| Example 2                                       | 133 |

| Example 3                                       |     |

| Danie Die Die Die Die Die Die Die Die Die D     | 101 |

**Appendix C: SPI-4.2 Lite Core Verification**

# Schedule of Figures

| Chapter 2: Core Architecture                                                                              |

|-----------------------------------------------------------------------------------------------------------|

| Figure 2-1: SPI-4.2 Lite Core in a Typical Link Layer Application                                         |

| Figure 2-2: Sink Core Block Diagram                                                                       |

| Figure 2-3: Source Core Block Diagram and I/O Interface Signals                                           |

|                                                                                                           |

| Chapter 3: Generating the Core                                                                            |

| Figure 3-1: SPI-4.2 Lite Sink and Source Main Customization Screen 44                                     |

| 1 game o 11 of 1 112 Effe of the unite obtains executive and objects 11 111 1111 1111 1111 1111 1111 1111 |

| Chapter 4: Designing with the Core                                                                        |

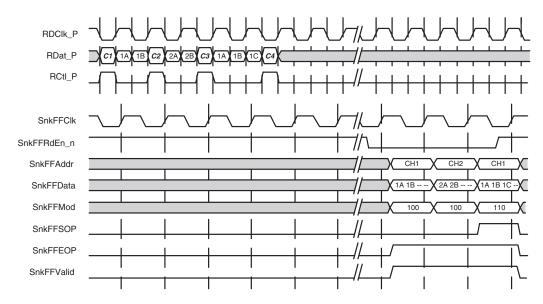

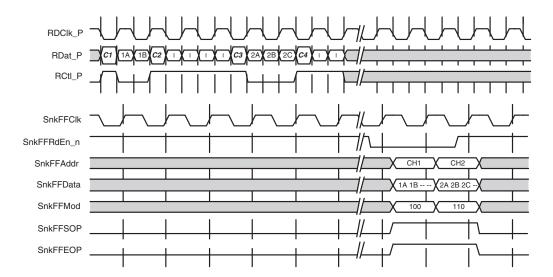

| Figure 4-1: SPI-4.2 Interface to the 64-Bit User Interface                                                |

| Figure 4-2: Sink Data Path - Short Packet Transfers with Minimum SOP Spacing                              |

| <b>Enforced</b> 55                                                                                        |

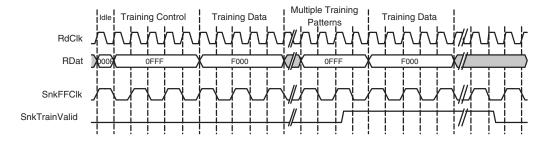

| Figure 4-3: Sink Training Valid Status                                                                    |

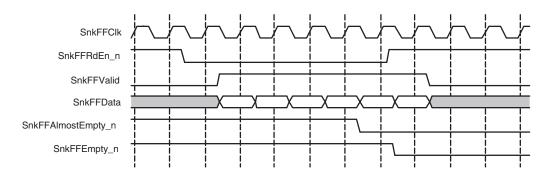

| Figure 4-4: Sink FIFO Almost Empty                                                                        |

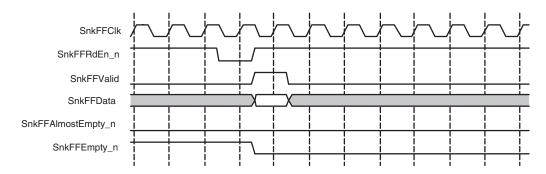

| Figure 4-5: Sink FIFO Empty                                                                               |

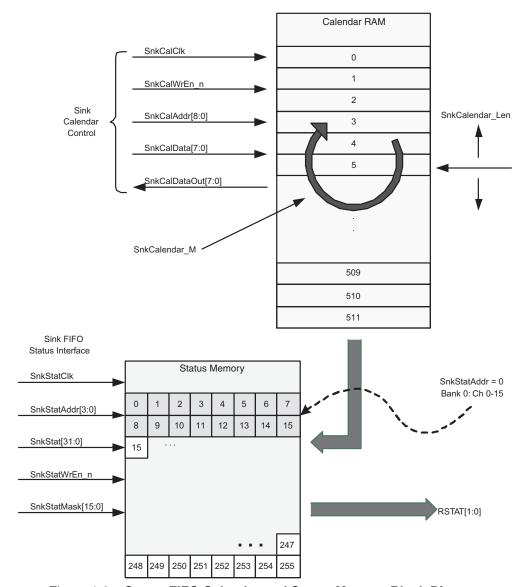

| Figure 4-6: Status FIFO Calendar and Status Memory Block Diagram 62                                       |

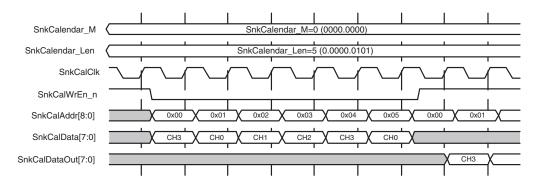

| Figure 4-7: Sink Calendar Initialization                                                                  |

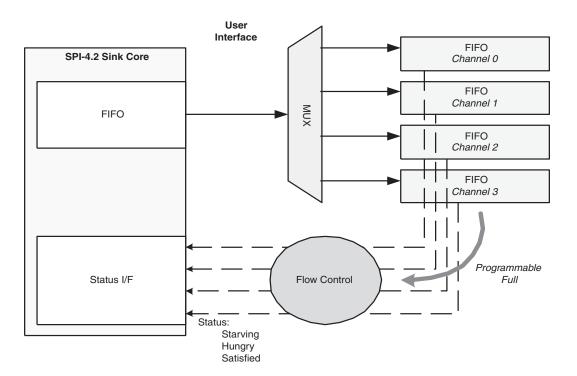

| Figure 4-8: Typical Flow Control Implementation for 4-Channel System 64                                   |

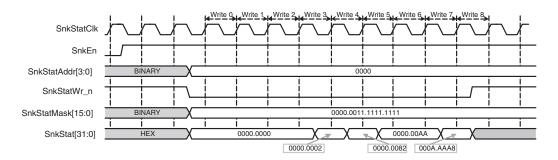

| Figure 4-9: Sink Status FIFO Interface Example 1: 10-channel Configuration 65                             |

| Figure 4-10: Sink Status FIFO Interface Example: 64-channel Configuration 66                              |

| Figure 4-11: Sink Status Path - User Interface to SPI-4.2 Interface 67                                    |

| Figure 4-12: FIFO Almost Full Mode "00"                                                                   |

| <i>Figure 4-13:</i> <b>FIFO Almost Full Mode "01"</b>                                                     |

| <i>Figure 4-14:</i> <b>FIFO Almost Full Mode "10" or "11"</b>                                             |

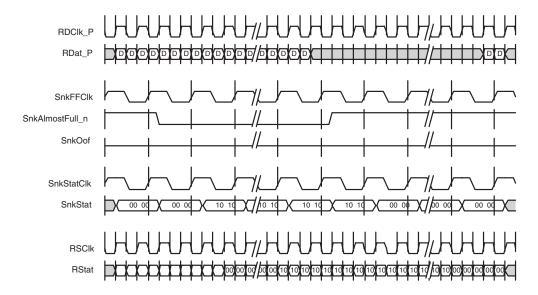

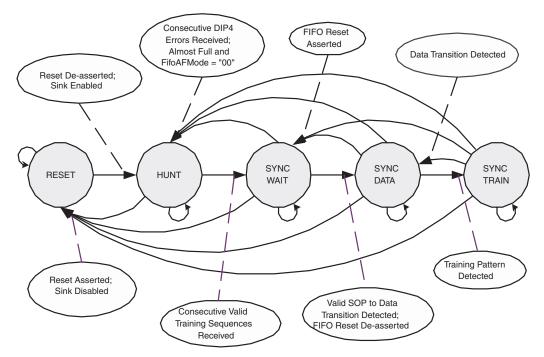

| Figure 4-15: Sink Startup Sequence State Machine71                                                        |

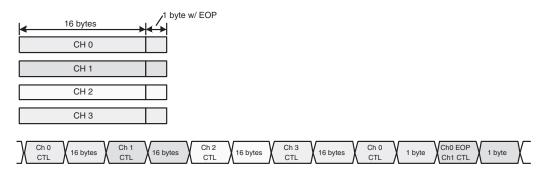

| Figure 4-16: Short Packet Support                                                                         |

| Figure 4-17: Sequential Payload Control Word Example                                                      |

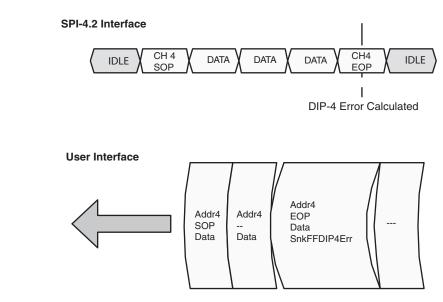

| Figure 4-18: Example of Error Flag SnkFFDIP4Err                                                           |

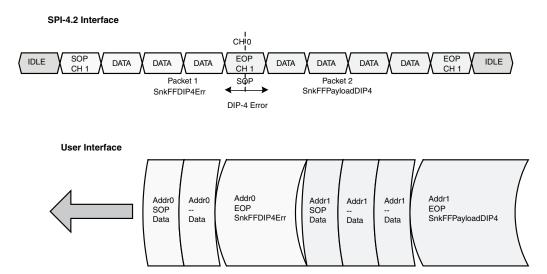

| Figure 4-19: Example of Error Flag SnkFFDIP4Err and SnkFFPayloadDIP4 75                                   |

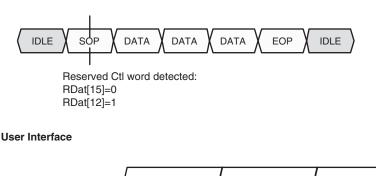

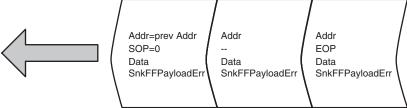

| Figure 4-20: Example of Error Flag SnkFFPayloadErr                                                        |

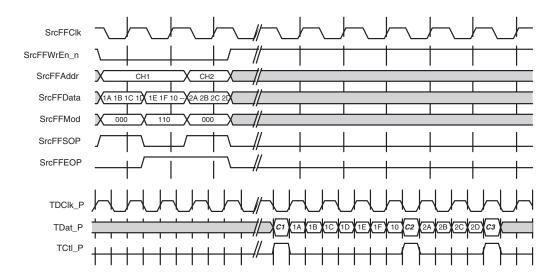

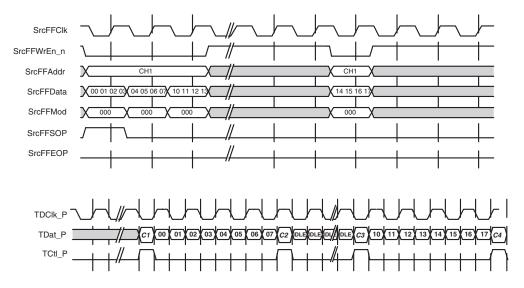

| Figure 4-21: Source Data Path: User Interface to SPI-4.2 Interface                                        |

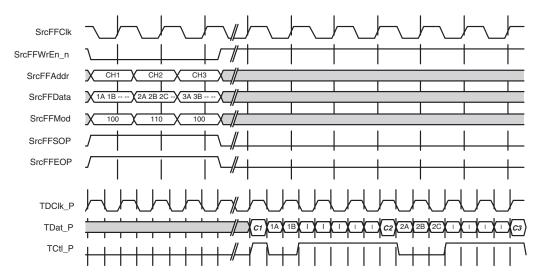

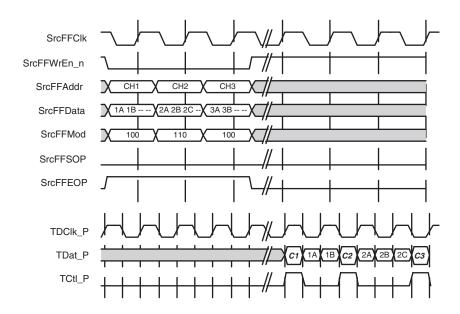

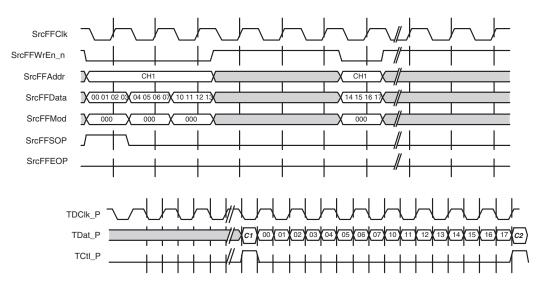

| Figure 4-22: Source Data Path - Minimum SOP Spacing Enforced                                              |

| Figure 4-23: Source Data Path - Short Packet Transfers                                                    |

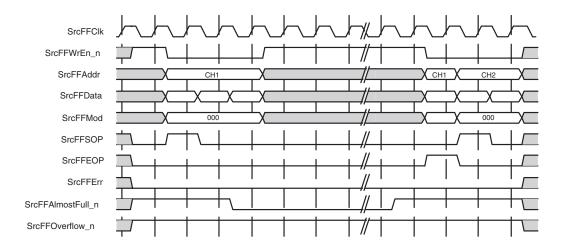

| Figure 4-24: Source FIFO Almost-full Condition                                                            |

| Figure 4-25: Source FIFO Overflow Condition                                                               |

| Figure 4-26: Writing to the Source FIFO                                                                   |

| Figure 4-27: Typical User Design Example                                                                  |

| Figure 4-28: Source Calendar Initialization                                                               |

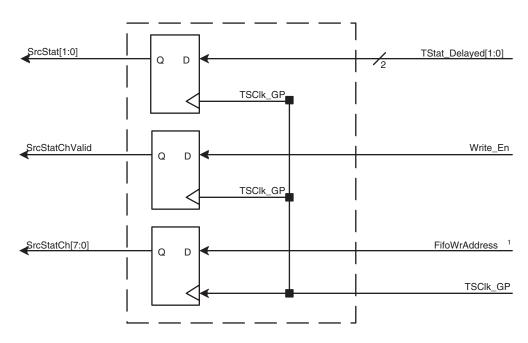

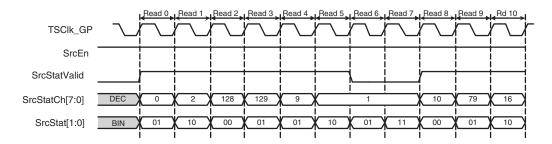

| Figure 4-29: Addressable Status FIFO Interface                                                            |

| Figure 4-30                                                                                     | : Addressable Status FIFO Interface: 4-Channel Configuration 8              | 39                               |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------|

| Figure 4-31                                                                                     | : Addressable Status FIFO Interface: 256-channel configuration              | 90                               |

| Figure 4-32                                                                                     | : Addressable Status FIFO Interface - SPI-4.2 Interface to User Interface 9 | 1                                |

| Figure 4-33                                                                                     | : Transparent Status FIFO Interface Block Diagram                           | 2                                |

| Figure 4-34                                                                                     | : Transparent Source Status FIFO Interface: 256-channel Configuration 9     | 13                               |

| Figure 4-35                                                                                     | : Example Of Source Burst Mode = 0                                          | 4                                |

| Figure 4-36                                                                                     | : Example Of Source Burst Mode = 1                                          | 4                                |

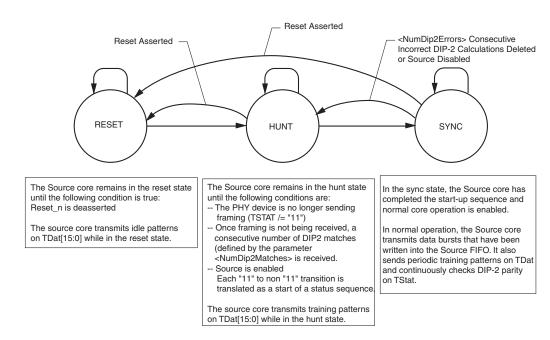

| Figure 4-37                                                                                     | : Source Startup Sequence State Machine                                     | )5                               |

|                                                                                                 |                                                                             |                                  |

| -                                                                                               | Special Design Considerations                                               | _                                |

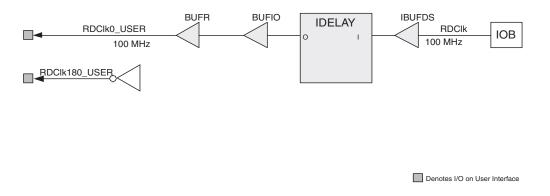

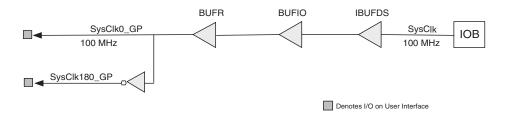

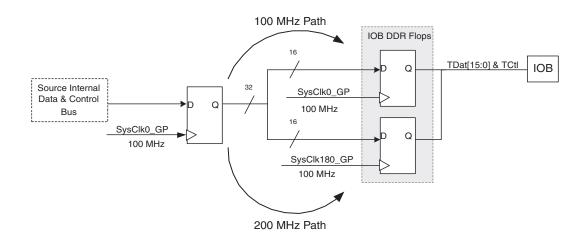

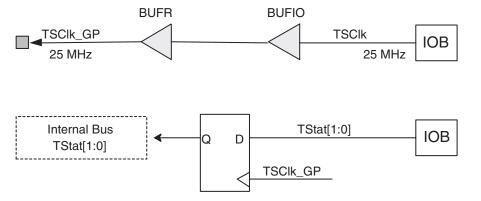

| Figure 6-1:                                                                                     | Embedded Clocking Option                                                    |                                  |

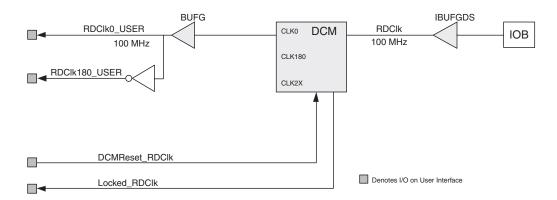

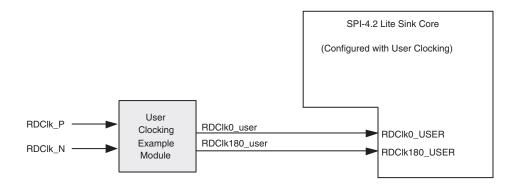

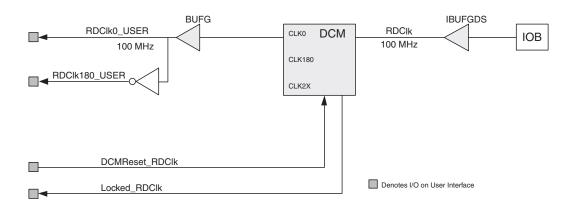

| Figure 6-1:<br>Figure 6-2:                                                                      | Embedded Clocking Option                                                    | 3                                |

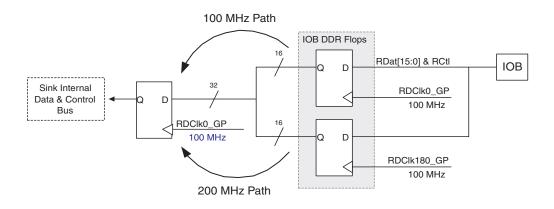

| Figure 6-1:<br>Figure 6-2:                                                                      | Embedded Clocking Option                                                    | 3                                |

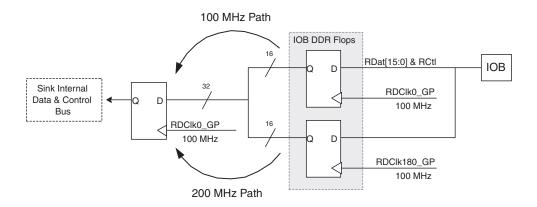

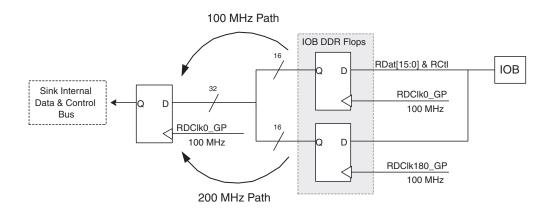

| Figure 6-1:<br>Figure 6-2:<br>Figure 6-3:                                                       | Embedded Clocking Option                                                    | 3<br>4                           |

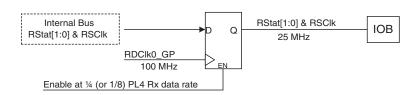

| Figure 6-1:<br>Figure 6-2:<br>Figure 6-3:<br>Figure 6-4:                                        | Embedded Clocking Option                                                    | 3<br>4<br>5                      |

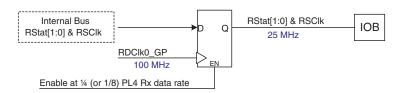

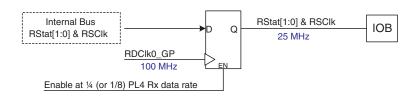

| Figure 6-1:<br>Figure 6-2:<br>Figure 6-3:<br>Figure 6-4:<br>Figure 6-5:                         | Embedded Clocking Option                                                    | 13<br>14<br>15                   |

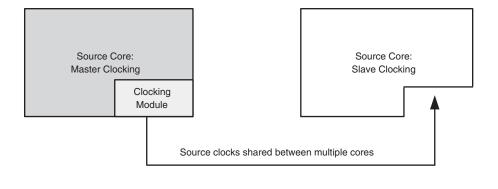

| Figure 6-1: Figure 6-2: Figure 6-3: Figure 6-4: Figure 6-5: Figure 6-6:                         | Embedded Clocking Option                                                    | 13<br>14<br>15<br>16             |

| Figure 6-1: Figure 6-2: Figure 6-3: Figure 6-4: Figure 6-5: Figure 6-6: Figure 6-7:             | Embedded Clocking Option                                                    | 13<br>14<br>15<br>16<br>17       |

| Figure 6-1: Figure 6-2: Figure 6-3: Figure 6-4: Figure 6-5: Figure 6-6: Figure 6-7: Figure 6-8: | Embedded Clocking Option                                                    | 13<br>14<br>15<br>16<br>17<br>18 |

# Schedule of Tables

| CI | hapter 2: Core Architecture                                                          |       |

|----|--------------------------------------------------------------------------------------|-------|

|    | Table 2-1: Sink SPI-4.2 Interface Signals                                            | 21    |

|    | Table 2-2: Sink Control and Status Signals                                           | 22    |

|    | Table 2-3: Sink FIFO Signals                                                         | 23    |

|    | Table 2-4: Sink Calendar Control Signals                                             | 25    |

|    | Table 2-5: Sink Status FIFO Signals                                                  | 25    |

|    | Table 2-6: Sink Static Configuration Signals                                         | 27    |

|    | Table 2-7: Sink Core Clocks: Embedded Clocking                                       | 29    |

|    | Table 2-8: Sink Core Clocks: Status Signals                                          | 29    |

|    | Table 2-9: Sink Core Clocks: User Clocking                                           | 30    |

|    | Table 2-10: Source SPI-4.2 Interface Signals                                         | 32    |

|    | Table 2-11: Source Control and Status Signals                                        | 33    |

|    | Table 2-12: Source FIFO Signals                                                      | 35    |

|    | Table 2-13: Source Calendar Control Signals                                          | 36    |

|    | Table 2-14: Source Status FIFO Signals                                               | 36    |

|    | Table 2-15: Source Static Configuration Signals                                      | 38    |

|    | Table 2-16:    Source Core Clocks: Master Configuration                              | 40    |

|    | Table 2-17: Source Core Clock Status Signals: Master Configuration                   | 40    |

|    | Table 2-18:    Source Core Clocks: Slave Configuration                               | 41    |

|    | hapter 3: Generating the Core hapter 4: Designing with the Core                      |       |

|    | Table 4-1: Formatting SPI-4.2 Interface Data (RDat) 64-bit User Interface (Example)  | 56    |

|    | Table 4-2: SPI-4.2 Control Word Mapping to 64-bit User Interface                     |       |

|    | Table 4-3: SPI-4.2 Control Word Mapping to 32-bit User Interface                     |       |

|    | Table 4-4: Status Written into SnkStat per Channel per Write Cycle                   |       |

|    | Table 4-5: Status Written to Status FIFO Interface                                   |       |

|    | Table 4-6: Example of Formatting Source FIFO Data for a 64-bit User Interface        | 79    |

|    | Table 4-7: SPI-4.2 Control Word Mapping to 32-bit Interface                          |       |

|    | Table 4-8: SPI-4.2 Control Word Mapping to 64-bit User Interface                     |       |

|    | Table 4-9: Status Written into SrcStat per Channel per Clock Cycle                   |       |

|    | Table 4-10: Status Read Summary                                                      |       |

|    | Table 4-11:         Status for the 256-channel Source Calendar Initialization System |       |

| CI | hapter 6: Special Design Considerations                                              |       |

|    | Table 6-1: Sink Core Embedded Clocking Resources                                     | . 111 |

|    | Table 6-2. Sink Core User Clocking Resources                                         | 113   |

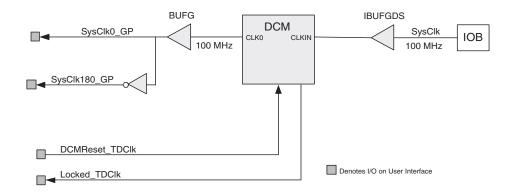

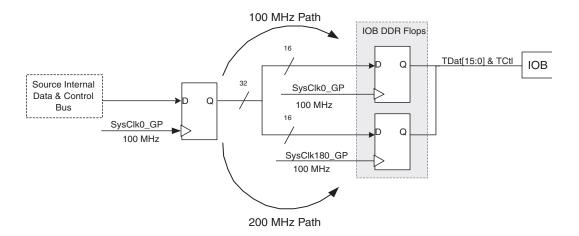

| Table 6-3: SysClk Clocking Resources        | 119 |

|---------------------------------------------|-----|

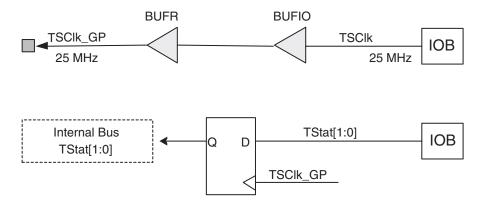

| Table 6-4: TSClk Clocking Resources         | 119 |

| Appendix A: SPI-4.2 Lite Control Word       |     |

| Table A-1: SPI-4.2 Lite Control Word Format | 131 |

## About This Guide

This user guide describes the function and operation of the Xilinx LogiCORE<sup>TM</sup> IP SPI-4.2 (PL4) Lite core, and provides information about designing, customizing, and implementing the core.

## **Contents**

This guide contains the following chapters:

- Preface, "About this Guide" describes the organization and purpose of the user guide and the conventions used in this document.

- Chapter 1, "Introduction" introduces the SPI-4.2 Lite core and provides related information, including recommended design experience, additional resources, technical support, and submitting feedback to Xilinx.

- Chapter 2, "Core Architecture" describes the SPI-4.2 Lite core architecture and interface signals.

- Chapter 3, "Generating the Core" describes how to generate the SPI-4.2 Lite core using the Xilinx CORE Generator<sup>TM</sup>.

- Chapter 4, "Designing with the Core" describes how to use the Xilinx SPI-4.2 Lite core in a user application.

- Chapter 5, "Constraining the Core" describes how to constrain the core.

- Chapter 6, "Special Design Considerations" describes how to instantiate multiple SPI 4.2 Lite cores in a design.

- Chapter 7, "Simulating and Implementing the Core" instructs you how to simulate and implement the SPI-4.2 Lite core in their design.

- Appendix A, "SPI-4.2 Lite Control Word" defines the SPI-4.2 control word format.

- Appendix B, "SPI-4.2 Lite Calendar Programming" contains examples that describe how to program calendars for the Source Status FIFO and Sink Status FIFO of the SPI-4.2 Lite core.

- Appendix C, "SPI-4.2 Lite Core Verification" describes the software verification of the SPI-4.2 Lite core.

## **Conventions**

This document uses the following conventions. An example illustrates each convention.

## Typographical

The following typographical conventions are used in this document:

| Convention          | Meaning or Use                                                                                               | Example                                                                                            |

|---------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Courier font        | Messages, prompts, and program files that the system displays                                                | speed grade: - 100                                                                                 |

| Courier bold        | Literal commands that you enter in a syntactical statement                                                   | ngdbuild design_name                                                                               |

| Helvetica bold      | Commands that you select from a menu                                                                         | File → Open                                                                                        |

|                     | Keyboard shortcuts                                                                                           | Ctrl+C                                                                                             |

|                     | Variables in a syntax<br>statement for which you must<br>supply values                                       | ngdbuild design_name                                                                               |

| Italic font         | References to other manuals                                                                                  | See the <i>Development System Reference Guide</i> for more information.                            |

|                     | Emphasis in text                                                                                             | If a wire is drawn so that it overlaps the pin of a symbol, the two nets are <i>not</i> connected. |

| Square brackets []  | An optional entry or parameter. However, in bus specifications, such as <b>bus[7:0]</b> , they are required. | ngdbuild [option_name] design_name                                                                 |

| Braces { }          | A list of items from which you must choose one or more                                                       | lowpwr ={on off}                                                                                   |

| Vertical bar        | Separates items in a list of choices                                                                         | lowpwr ={on off}                                                                                   |

| Vertical ellipsis   | Repetitive material that has been omitted                                                                    | IOB #1: Name = QOUT' IOB #2: Name = CLKIN'                                                         |

| Horizontal ellipsis | Repetitive material that has been omitted                                                                    | allow block block_name loc1 loc2 locn;                                                             |

## **Online Document**

The following conventions are used in this document:

| Convention            | Meaning or Use                                             | Example                                                                                                         |

|-----------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Blue text             | Cross-reference link to a location in the current document | See the section "Additional<br>Resources" for details.<br>Refer to "Title Formats" in<br>Chapter 1 for details. |

| Blue, underlined text | Hyperlink to a website (URL)                               | Go to <u>www.xilinx.com</u> for the latest speed files.                                                         |

## Introduction

The SPI-4.2 (PL4) Lite core implements and is functionally compliant to the *OIF-SPI-4-02.1* System Packet Interface Phase 2 specification and supports both VHDL and Verilog design environments.

This chapter introduces the SPI-4.2 Lite core and provides related information, including recommended design experience, additional resources, technical support, and how to submit feedback to Xilinx.

### **About the Core**

The SPI-4.2 Lite core is a Xilinx CORE Generator IP core, included in the latest IP Update on the Xilinx IP Center.

For detailed information about the core, see <a href="https://www.xilinx.com/products/ipcenter/DO-DI-POSL4MC.htm">www.xilinx.com/products/ipcenter/DO-DI-POSL4MC.htm</a>.

For information about system requirements, installation, and licensing options, see the *SPI-4.2 Lite Getting Started Guide*.

## **Recommended Design Experience**

Although the SPI-4.2 Lite core is a fully verified solution, the challenge associated with implementing a complete design varies depending on the configuration and functionality of the application. For best results, previous experience building high performance, pipelined FPGA designs using Xilinx implementation software and user constraints files (UCF) is recommended.

Contact your local Xilinx representative for a closer review and estimation for your specific requirements.

## **Additional Core Resources**

For detailed information and updates about the SPI-4.2 Lite core, see the following documents, located on the SPI-4.2 product lounge page at:

www.xilinx.com/ipcenter/posphyl4/spi42\_core.htm

- SPI-4.2 Lite Data Sheet

- SPI-4.2 Lite Release Notes

- SPI-4.2 Lite Getting Started Guide

## **Technical Support**

To obtain technical support specific to the SPI-4.2 Lite core, visit <a href="www.xilinx.com/support">www.xilinx.com/support</a>. Questions are routed to a team of engineers with expertise using the SPI-4.2 Lite core.

Xilinx will provide technical support for use of this product as described in the *SPI-4.2 Lite User Guide* and the *SPI-4.2 Lite Getting Started Guide*. Xilinx cannot guarantee timing, functionality, or support of this product for designs that do not follow these guidelines.

## **Feedback**

Xilinx welcomes comments and suggestions about the SPI-4.2 Lite core and the documentation provided with the core.

#### SPI-4.2 Lite Core

For comments or suggestions about the SPI-4.2 Lite core, please submit a webcase from <a href="https://www.xilinx.com/support/clearexpress/websupport.htm">www.xilinx.com/support/clearexpress/websupport.htm</a>. Be sure to include the following information:

- Product name

- Core version number

- Explanation of your comments

#### **Document**

For comments or suggestions about this document, please submit a WebCase from <a href="https://www.xilinx.com/support/clearexpress/websupport.htm">www.xilinx.com/support/clearexpress/websupport.htm</a>. Be sure to include the following information:

- Document title

- Document number

- Page number(s) to which your comments refer

- Explanation of your comments

## Core Architecture

This chapter describes the SPI-4.2 Lite core architecture and interface signals.

## **System Overview**

The SPI-4.2 Lite core is comprised of two separate cores that enable the transmission (Source core) and reception (Sink core) of data.

- **Sink Core.** Receives data from the SPI-4.2 interface. It takes the 16-bit interface and maps it to a 32-bit or 64-bit interface enabling the internal logic to run at a quarter of the line rate.

- **Source Core**. Transmits data on the SPI-4.2 interface. Payload data written into the core as 32-bit or 64-bit words (two or four 16-bit SPI-4.2 Lite words, respectively) is mapped onto the 16-bit SPI-4.2 interface.

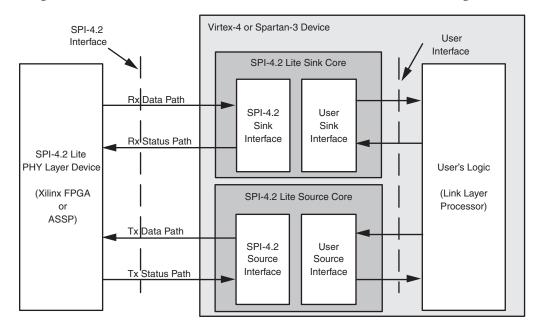

Figure 2-1 illustrates the interfaces of the SPI-4.2 Lite core and shows it in a typical link-layer application.

In the link layer example, the SPI-4.2 interface connects an external physical-layer device to a link-layer implemented in a Virtex<sup>TM</sup>-4 FPGA. The user logic reads data from the Sink core and writes data into the Source core. A standard FIFO interface is provided for this

data access and facilitates integration within a system. Dedicated signals are used to configure the Sink and Source cores in circuit and monitor a suite of status registers.

Figure 2-1: SPI-4.2 Lite Core in a Typical Link Layer Application

#### Sink Core

The Sink core receives data from the SPI-4.2 interface. It takes the 16-bit interface and maps it to a 32-bit or 64-bit interface enabling the internal logic to run at a half (for 32-bit) or an quarter (for 64-bit) of the line rate. The user data and the corresponding control signals are accessed with a standard FIFO interface. The FIFO read and write operations are performed in independent clock domains.

The Sink core implements the following features:

- Supports 32-bit or 64-bit user data width

- Dedicated output signal indicating loss of valid RDClk

- Provides a FIFO reset signal for clearing contents of the data pipe during operation

- Provides support for forcing the insertion of DIP-2 errors for system testing

- Regional clocking option (for Virtex-4 and Virtex-5 devices only, saves global clocking resources)

- Provides both embedded and user clocking options

For more information on core features, see Chapter 4, "Designing with the Core."

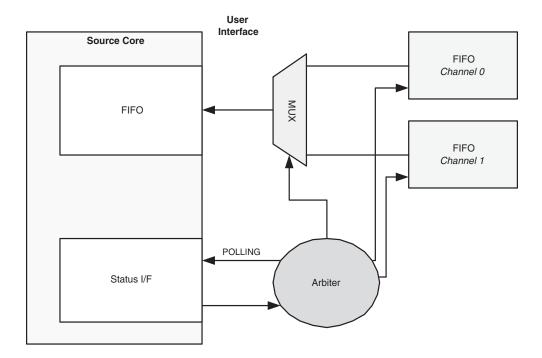

### Source Core

The Source core transmits data on the SPI-4.2 interface. Payload data written into the core as 32-bit or 64-bit words (two or four 16-bit SPI-4.2 Lite words, respectively) are mapped onto the 16-bit SPI-4.2 interface. While packet data written into the core may not be 32-bit or 64-bit aligned, the core optimally maps the data to 16-bit words such that no filler idle cycles are inserted. The data along with the control signals are written into the core via a

standard FIFO interface, and the FIFO read and write operations are performed in independent clock domains.

The Source core implements the following features:

- Supports 32-bit or 64-bit user data width.

- Optionally transmits only complete data bursts.

- Provides both master and slave clocking to facilitate multiple core implementations.

- Enables addressable or transparent access to SPI-4.2 flow control data.

- Provides a FIFO reset signal for clearing contents of the data pipe during operation.

- Provides support for forcing the insertion of DIP-4 errors for system testing.

For more information on core features, see Chapter 4, "Designing with the Core."

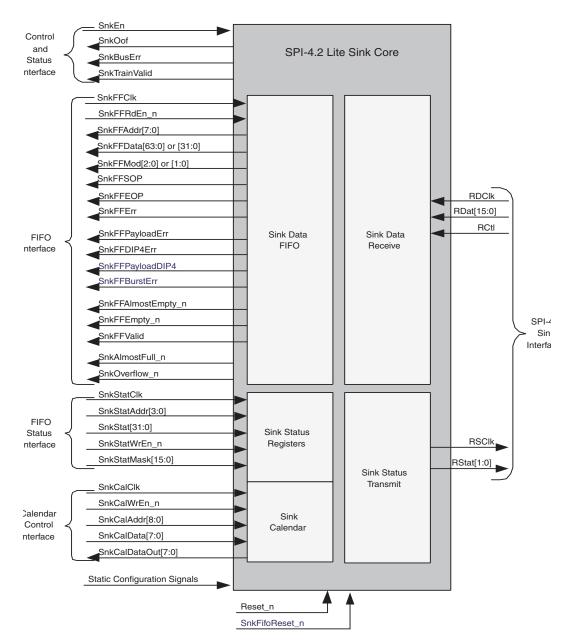

## **Sink Core Interfaces**

The Sink core has five functional modules:

- Sink Data FIFO

- Sink Data Receive

- Sink Status Registers

- Sink Calendar

- Sink Status Transmit

The Sink core has the following interfaces:

- Sink SPI-4.2 Interface

- Sink User Interface

- ♦ Sink Control and Status Interface

- ♦ Sink FIFO Interface

- Sink Status and Flow Control Interface

- Calendar Control Interface

- Status FIFO Interface

- Sink Configuration Interface

- ♦ Sink Clocking Interface

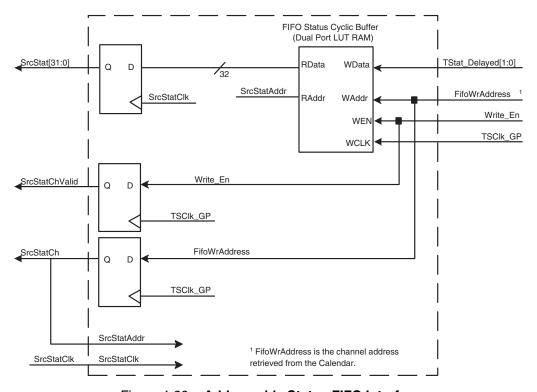

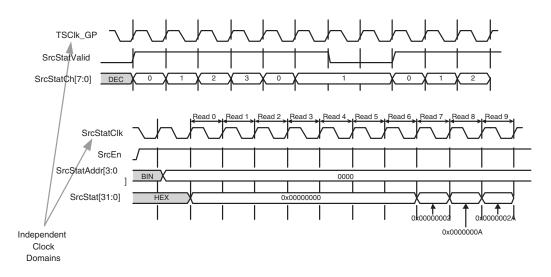

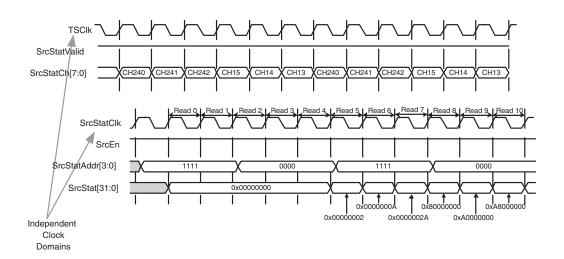

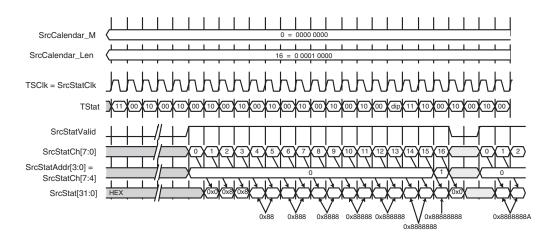

The functional modules and signals which comprise the different interfaces are shown in Figure 2-2 and defined in tables in the following sections.

Figure 2-2: Sink Core Block Diagram

#### Sink SPI-4.2 Interface

The SPI-4.2 interface uses LVDS I/O buffers to receive 16-bit data words. The 16-bit data words received on the SPI-4.2 interface are combined into 32-bit or 64-bit data words by the SPI-4.2 Lite core, which allows the user interface to run at a half (32-bit interface) or quarter (64-bit interface) of the data rate. For example, for a 200 Mbps data rate and a 32-bit interface, you can read data from the Sink core at 100 MHz, and if a 64-bit interface is used, you can read data from the Sink core at 50 MHz and maintain the same data rate.

The resulting data words are written into an asynchronous FIFO. The received 16-bit control words are stored out of band in the FIFO, along with the corresponding data word. The received control words that are not idle or training words can contain the information listed below:

- Start or continuation of the following packet

- Link address of the following packet

- End of the preceding packet

- Number of valid bytes in the last word of the preceding packet

- Error conditions in the preceding packet

In addition to receiving 16-bit data words, the SPI-4.2 interface also sends flow control data at 1/4 rate (or 1/8 rate) of its data interface. The 32-bit status (2-bit status for each channel) from the user interface is processed and formatted by the SPI-4.2 Lite core to be transmitted on RStat. Table 2-1 defines the Sink SPI-4.2 interface signals.

Table 2-1: Sink SPI-4.2 Interface Signals

| Name                         | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                                           |

|------------------------------|-----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDClk_P<br>RDClk_N           | Input     | n/a             | SPI-4.2 Receive Data Clock (LVDS): Source synchronous clock received with RDat and RCtl. The rising and falling edges of this clock (DDR) are used to clock RDat and RCtl.                                                                                            |

| RDat_P[15:0]<br>RDat_N[15:0] | Input     | RDClk           | <b>SPI-4.2 Receive Data Bus</b> (LVDS): The 16-bit data bus used to receive SPI-4.2 data and control information.                                                                                                                                                     |

| RCtl_P<br>RCtl_N             | Input     | RDClk           | <b>SPI-4.2 Receive Control</b> (LVDS): Signal that indicates whether data or control information is present on the RDat bus. When RCtl is deasserted, data is present on RDat. When RCtl is asserted, control information is present on RDat.                         |

| RSClk                        | Output    | n/a             | SPI-4.2 Receive Status Clock: Source synchronous clock transmitted with RStat at 1/2 or 1/4 rate of the RDClk. The rate of the status clock is controlled by the static configuration signal RSClkDiv. You can select this signal to be transmitted as LVTTL or LVDS. |

| RStat[1:0]                   | Output    | RSClk           | <b>SPI-4.2 Receive FIFO Status</b> : FIFO Status Channel flow control interface. You can select this bus to be transmitted as LVTTL or LVDS.                                                                                                                          |

### Sink User Interface

The Sink User Interface includes all signals other than those on the SPI-4.2 Interface. The high-performance logic on the Sink back-end enables the user interface to run at higher frequencies than the SPI-4.2 Interface. This is sometimes required if a large percentage of the traffic consists of small packets.

The User Interface is subdivided into five smaller interfaces. Each of these interfaces are presented in detail below:

- Control and Status Interface: The signals of this interface apply to the operation of the Sink core.

- **FIFO Interface**: The signals of this interface allow you to access data received on the SPI-4.2 Interface.

- **Status and Flow Control Interface**: The signals of this interface send flow control information on the SPI-4.2 Interface.

- **Static Configuration Interface**: The signals of this interface allow you to configure the core.

- **Clocking Interface**: The signals of this interface report the status of the clocks and include the general purpose clocks.

#### Sink Control and Status Interface

The Sink core control and status signals either control the operation of the entire Sink core or provide status information that is not associated with a particular channel (port) or packet. Table 2-2 defines the Sink control and status signals.

Table 2-2: Sink Control and Status Signals

| Name           | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|-----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset_n        | Input     | n/a             | Reset: Active Low signal that asynchronously initializes internal flip-flops, registers, and counters. When Reset_n is asserted, the Sink core will go out of frame and the entire data path is cleared (including the FIFO). The Sink core will also assert SnkOof, and deassert SnkBusErr and SnkTrainValid. When Reset_n is asserted, the Sink core will transmit framing "11" on RStat and continue to drive RSClk.  Following the deassertion of Reset_n, the sink calendar should be programmed if the calendar is initialized in-circuit. |

| SnkFifoReset_n | Input     | SnkFFClk        | <b>Sink FIFO Reset:</b> Active low signal enables you to reset the Sink FIFO and the associated data path logic. This enables the FIFO to be cleared while remaining in frame.                                                                                                                                                                                                                                                                                                                                                                   |

|                |           |                 | Coming out of SnkFifoReset_n, the Sink core will discard all data on the SPI-4.2 interface until a valid SOP control word is received.                                                                                                                                                                                                                                                                                                                                                                                                           |

| SnkEn          | Input     | SnkStatClk      | <b>Sink Enable:</b> Active high signal that enables the Sink core. When SnkEn is deasserted, the Sink core will go out of frame and will not store any additional data in the FIFO. The current contents of the FIFO remain intact.                                                                                                                                                                                                                                                                                                              |

|                |           |                 | The Sink core will also assert SnkOof, and deassert SnkBusErr and SnkTrainValid. When SnkEn is deasserted, the Sink core will transmit framing "11" on RStat and continue to drive RSClk.                                                                                                                                                                                                                                                                                                                                                        |

Table 2-2: Sink Control and Status Signals (Continued)

| Name               | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                                                                                       |

|--------------------|-----------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SnkOof             | Output    | SnkFFClk        | <b>Sink Out-of-Frame</b> : Active high signal that indicates that the SPI-4.2 Lite Sink block is not in frame. This signal is asserted when SnkEn is deasserted or the Sink block loses synchronization with the data received on the SPI-4.2 Interface. This signal is deasserted once the Sink block reacquires synchronization with the received SPI-4.2 data. |

| SnkBusErr          | Output    | SnkFFClk        | <b>Sink Bus Error:</b> Active high signal that indicates SPI-4.2 protocol violations or bus errors that are not associated with a particular packet. Information on the specific error condition that caused the SnkBusErr assertion is provided on SnkBusErrStat                                                                                                 |

| SnkBusErrStat[7:0] | Output    | SnkFFClk        | <b>Sink Bus Error Status</b> : Each bit of this bus corresponds to a specific Sink Bus Error condition and is asserted concurrently with SnkBusErr. The error conditions detected are reported as follows:                                                                                                                                                        |

|                    |           |                 | SnkBusErrStat [0]: Minimum SOP spacing violation                                                                                                                                                                                                                                                                                                                  |

|                    |           |                 | SnkBusErrStat [1]: Control word with EOP not preceded by a data word                                                                                                                                                                                                                                                                                              |

|                    |           |                 | SnkBusErrStat [2]: Payload control word not followed by a data word                                                                                                                                                                                                                                                                                               |

|                    |           |                 | SnkBusErrStat [3]: DIP4 error received during training or on idles                                                                                                                                                                                                                                                                                                |

|                    |           |                 | SnkBusErrStat [4]: Reserved control words received                                                                                                                                                                                                                                                                                                                |

|                    |           |                 | SnkBusErrStat [5]: Non-zero address bits on control words received (except on payload and training control words)                                                                                                                                                                                                                                                 |

|                    |           |                 | SnkBusErrStat [6:7]: Reserved bits (tied low)                                                                                                                                                                                                                                                                                                                     |

| SnkTrainValid      | Output    | SnkFFClk        | <b>Sink Training Valid:</b> Active high signal that indicates that a valid training pattern has been received. This signal is asserted for the duration of the training pattern (20 SPI-4.2 bus clock cycles or 5 RDClk0_GP clock cycles), if the training pattern received is successfully decoded.                                                              |

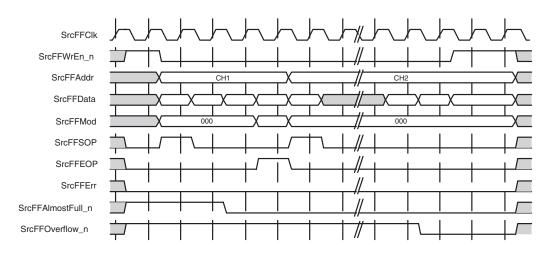

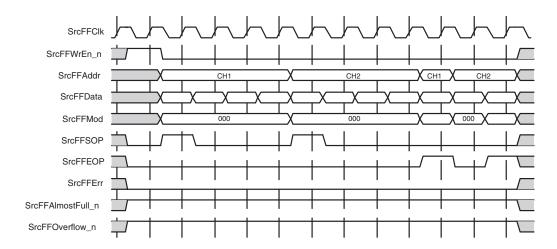

### Sink FIFO Interface

The Sink FIFO Interface signals allow you to access the data (received on the SPI-4.2 Interface) that is stored in the FIFO. The signals on this interface is defined in Table 2-3.

Table 2-3: Sink FIFO Signals

| Name                                     | Direction | Description                                                                                                                                                                                                                       |

|------------------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SnkFFClk                                 | Input     | <b>Sink FIFO Clock</b> : All Sink FIFO Interface signals are synchronous to the rising edge of this clock.                                                                                                                        |

| SnkFFRdEn_n                              | Input     | <b>Sink FIFO Read-Enable</b> : When detected low at the rising edge of SnkFFClk, data and status information is available from the FIFO on the next rising edge of SnkFFClk.                                                      |

| SnkFFAddr[7:0]                           | Output    | Sink FIFO Channel Address: Channel number associated with the data on SnkFFData.                                                                                                                                                  |

| SnkFFData[31:0]<br>or<br>SnkFFData[63:0] | Output    | <b>Sink FIFO Data Out</b> : The Sink FIFO data bus. Bit 0 is the LSB.  The core can be configured to have a 32- or 64-bit Interface. The 64-bit interface enables running at half the clock rate required for a 32-bit interface. |

| SnkFFMod[1:0]<br>or<br>SnkFFMod[2:0]     | Output    | Sink FIFO Modulo: This signal indicates which bytes on the SnkFFData bus are valid when the SnkFFEOP signal is asserted.  SnkFFMod[1:0] is used with a 32-bit interface.  SnkFFMod[2:0] is used with a 64-bit interface.          |

Table 2-3: Sink FIFO Signals (Continued)

| Name               | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|--------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SnkFFSOP           | Output    | <b>Sink FIFO Start of Packet</b> : When asserted (active high), this signal indicates the start of a packet is being read out of the Sink FIFO.                                                                                                                                                                                                                                                                                                                                                                                              |  |

| SnkFFEOP           | Output    | <b>Sink FIFO End of Packet</b> : When asserted (active high), this signal indicates that the end of a packet is being read out of the Sink FIFO.                                                                                                                                                                                                                                                                                                                                                                                             |  |

| SnkFFErr           | Output    | <b>Sink FIFO Error</b> : When asserted (active high), this signal indicates that the current packet is terminated with an EOP abort condition. This signal is only asserted when SnkFFEOP is asserted.                                                                                                                                                                                                                                                                                                                                       |  |

| SnkFFEmpty_n       | Output    | <b>Sink FIFO Empty</b> : When asserted (active low), this signal indicates that the Sink FIFO is empty. No data can be read until this signal is deasserted. This signal is asserted with the last data word read out of the FIFO.                                                                                                                                                                                                                                                                                                           |  |

| SnkFFAlmostEmpty_n | Output    | Sink FIFO Almost Empty: When this signal is asserted (active low), it indicates that one word remains in the FIFO, and you should deassert the read enable signal on the next clock cycle. The user's read logic should evaluate the SnkFFEmpty_n signal to verify that there is no data in the FIFO in case an additional word was simultaneously written into the FIFO. An example of the behavior of this interface signal is provided with the SPI-4.2 Lite core in the Design Example (see the pl4_lite_fifo_loopback_read.v/vhd file.) |  |

| SnkFFValid         | Output    | <b>Sink FIFO Read Valid</b> : When asserted (active high), this signal indicates that the information on SnkFFData, SnkFFAddr, SnkFFSOP, SnkFFEOP, SnkFFBurstErr, SnkFFMod, SnkFFErr, SnkFFDIP4Err, and SnkFFPayloadErr is valid.                                                                                                                                                                                                                                                                                                            |  |

| SnkFFDIP4Err       | Output    | <b>Sink FIFO DIP-4 Error:</b> When asserted (active high), this signal indicates that a DIP-4 parity error was detected with the SPI-4.2 control word ending a packet or burst of data. This signal is asserted at the end of that packet or burst of data.                                                                                                                                                                                                                                                                                  |  |

| SnkFFPayloadDIP4   | Output    | <b>Sink FIFO Payload DIP4 Error:</b> When asserted (active high), this signal indicates that DIP-4 parity error was detected with the SPI-4.2 control word starting a packet or burst of data. This signal is asserted at the end of that packet or burst of data.                                                                                                                                                                                                                                                                           |  |

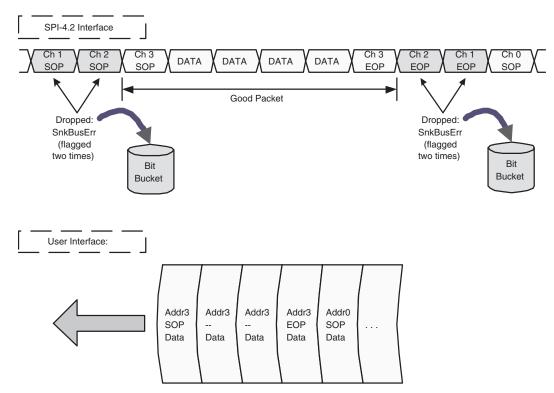

| SnkFFBurstErr      | Output    | Sink FIFO Burst Error: When asserted (active high), this signal indicates that the Sincore has received data that was terminated on a non-credit boundary without an EC SnkFFBurstErr may be used by the user's logic to indicate missing EOPs, or incorrect terminated bursts. In this case the Sink core does not assert SnkFFEOP or SnkFFETr.                                                                                                                                                                                             |  |

| SnkFFPayloadErr    | Output    | Sink FIFO Payload Error: When asserted (active high), this signal indicates that the received data was not preceded by a valid payload control word. Since it is not clear what the packet Address and SOP should be, it is flagged as an error. This is asserted with each data word coming out of the FIFO, and will remain asserted until a valid payload control word is followed by data.                                                                                                                                               |  |

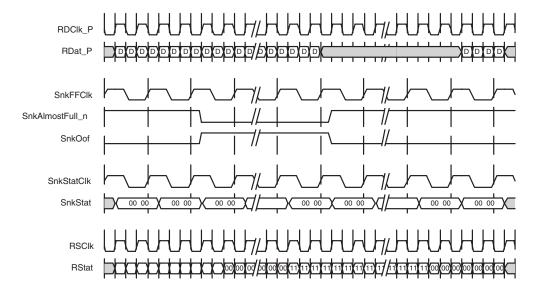

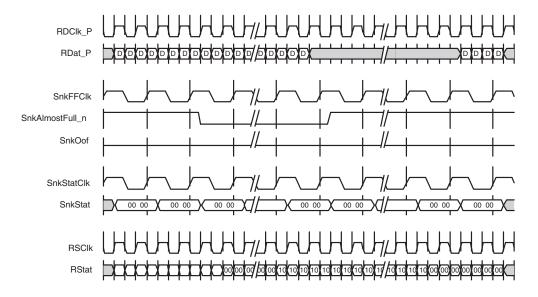

| SnkAlmostFull_n    | Output    | <b>Sink Almost Full</b> : When asserted (active low), this signal indicates that the Sink core is approaching full (as defined by the parameter SnkAFThresAssert), and that immediate action should be taken to prevent overflow.                                                                                                                                                                                                                                                                                                            |  |

| SnkOverflow_n      | Output    | <b>Sink Overflow:</b> When asserted (active low), this signal indicates that the Sink core has overflowed and is in an error condition. Data will be lost if SnkOverflow_n is asserted, since no data is written into the FIFO when the overflow signal is asserted.                                                                                                                                                                                                                                                                         |  |

## Sink Status and Flow Control Interface (Calendar Control and Status FIFO)

The Sink Status and Flow Control interface enables you to send flow control data on the SPI-4.2 Interface. The status information is sent based on the channel order and channel frequency defined in the programmable calendar. Table 2-4 and Table 2-5 define the calendar interface and status FIFO interface signals.

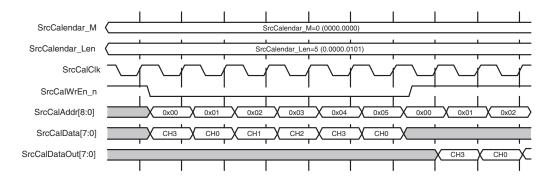

Table 2-4: Sink Calendar Control Signals

| Name               | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                                                  |

|--------------------|-----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SnkCalClk          | Input     | n/a             | <b>Sink Calendar Clock:</b> All Sink calendar signals are synchronous to this clock.                                                                                                                                                                                         |

| SnkCalWrEn_n       | Input     | SnkCalClk       | Sink Calendar Write Enable: When this signal is asserted (active low), the Sink Calendar is written with the data on the SnkCalData bus on the rising edge of SnkCalClk. When the signal is deasserted, the Sink Calendar data can be read on SnkCalDataOut.                 |

| SnkCalAddr[8:0]    | Input     | SnkCalClk       | Sink Calendar Address: When SnkCalWrEn_n is asserted, this bus indicates the calendar address to which the data on SnkCalData is written. When SnkCalWrEn_n is deasserted, this bus indicates the calendar address from which the channel number on SnkCalDataOut is driven. |

| SnkCalData[7:0]    | Input     | SnkCalClk       | Sink Calendar Data: This bus contains the channel number to write into the calendar buffer when SnkCalWrEn_n is enabled. The channel numbers written into the calendar indicate the order that status is sent on RStat.                                                      |

| SnkCalDataOut[7:0] | Output    | SnkCalClk       | Sink Calendar Data Output: This bus contains the channel number that is read from the calendar buffer when SnkCalWrEn_n is disabled. The channel numbers read from the calendar indicate the order that status is sent on RStat.                                             |

Table 2-5: Sink Status FIFO Signals

| Name              | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                 |

|-------------------|-----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SnkStatClk        | Input     | n/s             | <b>Sink Status Clock:</b> All Sink Status write signals are synchronous to this clock.                                                                                                                                                      |

| SnkStat[31:0]     | Input     | SnkStatClk      | <b>Sink Status Bus:</b> This 32-bit bus is used to write status information into the Status FIFO. You can write the status for 16 channels each clock cycle.                                                                                |

|                   |           |                 | The 16-channel status that are accessed simultaneously are grouped in the following manner: channels 15 to 0, channels 31 to 16, channels 47 to 32, , channels 255 to 239.                                                                  |

| SnkDIP2ErrRequest | Input     | SnkStatClk      | <b>Sink DIP2 Error Request:</b> This is an active high signal that requests an incorrect DIP-2 to be sent out of the RStat bus. When this signal is asserted, Sink Status FIFO responds by inverting the next DIP2 value that it transmits. |

Table 2-5: Sink Status FIFO Signals (Continued)

| Name              | Direction | Clock<br>Domain | Description                                                                                                                                                                                                                                                                                                  |

|-------------------|-----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SnkStatAddr[3:0]  | Input     | SnkStatClk      | <b>Sink Status Address bus</b> : The Sink Status Address determines the group of 16-channel status that SnkStat will be updating.                                                                                                                                                                            |

|                   |           |                 | Bank 0: SnkStatAddr=0, channels 15 to 0                                                                                                                                                                                                                                                                      |

|                   |           |                 | Bank 1: SnkStatAddr=1, channels 31 to 16                                                                                                                                                                                                                                                                     |

|                   |           |                 | Bank 2: SnkStatAddr=2, channels 47 to 32                                                                                                                                                                                                                                                                     |

|                   |           |                 |                                                                                                                                                                                                                                                                                                              |

|                   |           |                 | Bank 15: SnkStatAddr=15, channels 255 to 239                                                                                                                                                                                                                                                                 |

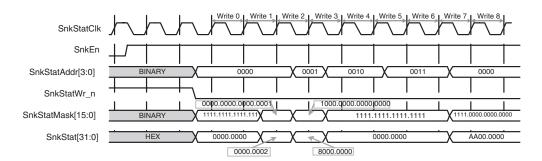

| SnkStatWr_n       | Input     | SnkStatClk      | Sink Status Write: The Sink Status Write (active low) qualifies the SnkStatMask signal. When SnkStatWr_n is asserted (active low), status for the different channels is updated. When SnkStatWr_n is deasserted (active high), SnkStat input is ignored.                                                     |

| SnkStatMask[15:0] | Input     | SnkStatClk      | Sink Status Mask Bus: The Sink Status Mask determines if the 2-bit status among the corresponding group of 16 channels of status on SnkStat (being addressed by SnkStatAddr) will be updated when SnkStatWr_n is asserted (active low):                                                                      |

|                   |           |                 | SnkStatMask[x] = 1, status for channel (x+( $SnkStatAddr*16$ )) will be updated.                                                                                                                                                                                                                             |

|                   |           |                 | $SnkStatMask[y] = 0, status \ for \ channel \ (y+(SnkStatAddr*16)) \ will \ not be \ updated.$                                                                                                                                                                                                               |

|                   |           |                 | For example, if SnkStatMask[15] = 1 and SnkStatAddr = 1, then SnkStat[31:30] = 00 will overwrite the current status on channel 31. If SnkStatMask is all zeros, none of the sixteen 2-bit status values will be updated. If SnkStatMask is all ones, all sixteen of the 2-bit status values will be updated. |

### Sink Static Configuration Interface

These signals are inputs to the core that are statically driven by setting them to a constant value in the top-level wrapper file. The SPI-4.2 Lite release includes a wrapper file that has the static configuration signals connected to the values selected in the CORE Generator GUI. Customization of these signals can be done using the GUI.

Two of the Sink Static Configuration signals can be changed in circuit. There are static registers for <code>SnkCalendar\_M</code> and <code>SnkCalendar\_Len</code> that are synchronous to <code>SnkStatClk</code>. To change these parameters while the core is operational, <code>SnkEn</code> must first be deasserted.

If you sets the configuration signal to an illegal number, the core is automatically set to the minimum value. Table 2-6 defines the Sink Static Configuration signals.

Table 2-6: Sink Static Configuration Signals

| Name                   | Direction       | Range                                                                         | Description                                                                                                                                                                                                                                                                                                                                                             |

|------------------------|-----------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NumDip4Errors[3:0]     | Static<br>Input | 1-15<br>Value of 0 is set to 1                                                | Number of DIP-4 Errors: The Sink Interface will go out-of-frame (assert SnkOof) and stop accepting data from the SPI-4.2 bus after receiving NumDip4Errors consecutive DIP-4 errors.                                                                                                                                                                                    |

| NumTrainSequences[3:0] | Static<br>Input | 1-15<br>Value of 0 is set to 1                                                | Number of Complete Training Sequences: A complete training pattern consists of 10 training control words and 10 training data words. The Sink interface requires NumTrainSequences consecutive training patterns before going in frame (deasserting SnkOof) and accepting data from the SPI-4.2 bus.                                                                    |

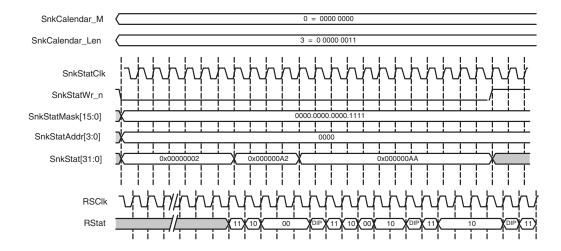

| SnkCalendar_M[7:0]     | Input           | 0-255<br>(effective range 1-256)                                              | <b>Sink Calendar Period</b> : The SnkCalendar_M parameter sets the number of repetitions of the calendar sequence before the DIP-2 parity and framing words are inserted.                                                                                                                                                                                               |

|                        |                 |                                                                               | The core implements this parameter as a static register synchronous to SnkStatClk, and it can be updated in circuit by first deasserting SnkEn.                                                                                                                                                                                                                         |

|                        |                 |                                                                               | Note that the Sink Calendar Period equals SnkCalendar_M + 1. For example, if SnkCalendar_M=22, the Sink Calendar Period will be equal to 23.                                                                                                                                                                                                                            |

| SnkCalendar_Len[8:0]   | Input           | 0-511<br>(effective range 1-512)                                              | Sink Calendar Length: The SnkCalendar_Len parameter sets the length of the calendar sequence. The core implements this parameter as a static register synchronous to SnkStatClk, and it can be updated in circuit by first deasserting SnkEn.                                                                                                                           |

|                        |                 |                                                                               | Note that the Sink Calendar Length equals<br>SnkCalendar_Len + 1. For example, if<br>SnkCalendar_Len=15, the Sink Calendar Length will<br>be equal to 16.                                                                                                                                                                                                               |